# Designing Foundry-Compatible Photonic Components and Circuits

Presented by:

Greg Baethge, Team Lead – Photonics Application Engineering Ansys Lumerical

July 13<sup>th</sup>, 2025

#### This session

- Foundry-compatible Photonic Design Today (format: slides. 10 minutes)

- Custom design: What is it and why is it challenging?

- Process-enabled custom component design

- Tower Semiconductor and Ansys foundrycompatible solution

- Design Case: Custom Ring Modulator for DWDM Transceiver (format: slides. 10 minutes)

- Designing custom ring modulator using foundry process file

- Calibrated compact model generation with CML Compiler

- Circuit simulation with foundry components and custom components

- Walkthrough / Demo (format: Demo, slides. 60 minutes)

- Step 1 Working with Lumerical UI

- Steps 2-5 Photonic Component Simulation

- Step 6 Custom Compact models

- Quick Mention (Step 7) Photonic Circuit

Simulation

- Q&A (10 minutes)

# Custom Component Design for Photonic Integrated Circuit (PIC)

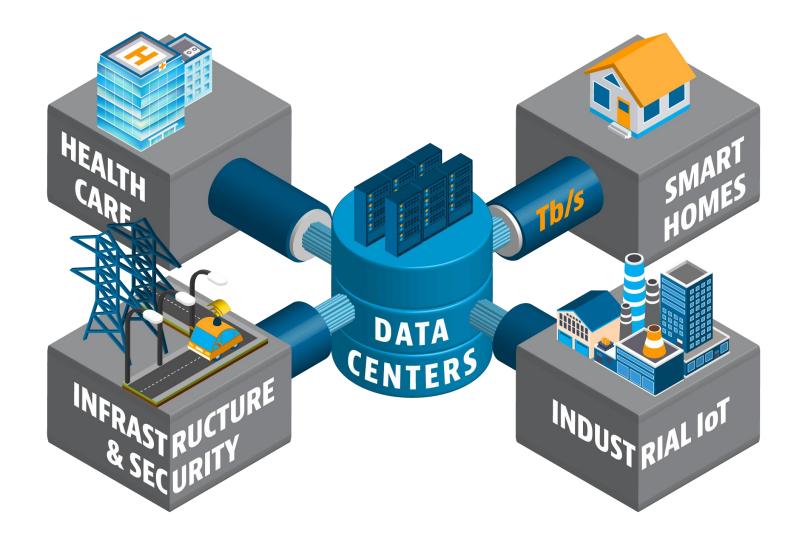

# Photonics is Everywhere and Growing!

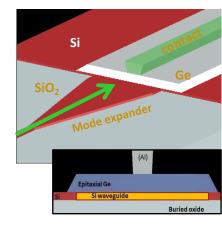

## **Building Blocks Beyond Waveguides**

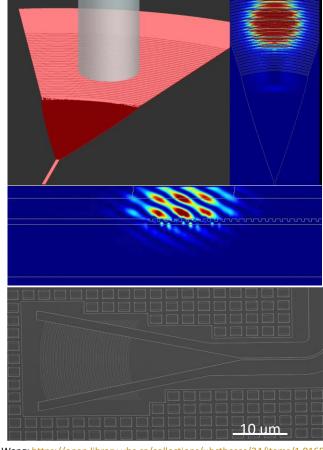

#### Waveguide coupling/splitting

Ring resonators

Fiber-waveguide coupling

X. Wang: https://open.library.ubc.ca/collections/ubctheses/24/items/1.0165738

Electrical phase control

Thermal phase control

Photodetector

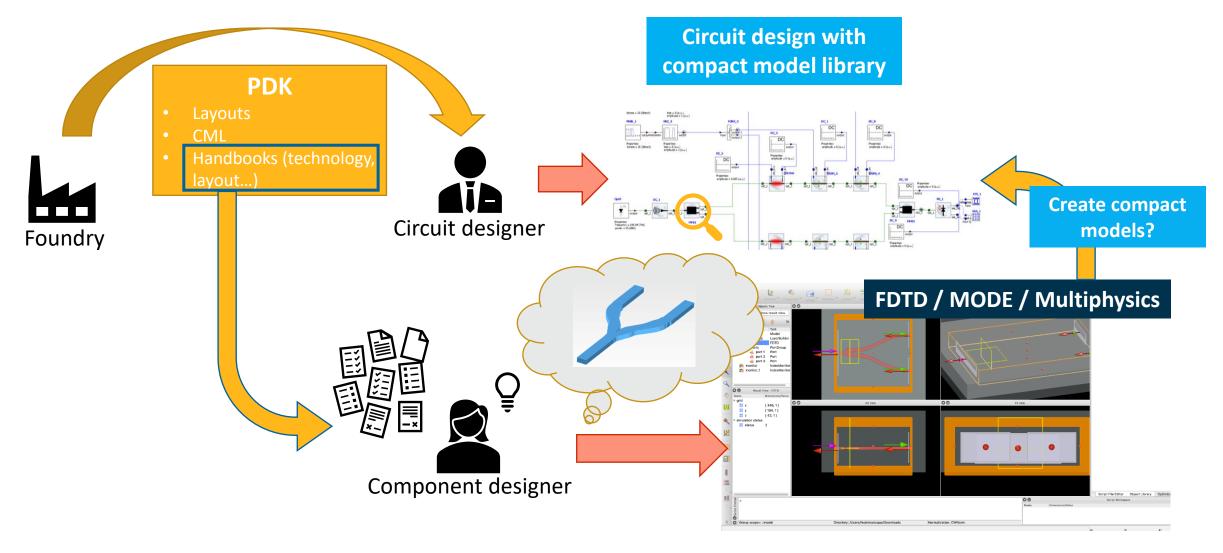

## The two challenges of custom component design

- 1. Creating the custom component according to the foundry's process.

- 2. Creating the compact model for this the custom component.

Powering Innovation That Drives Human Advancement

## Why is Custom Design Challenging?

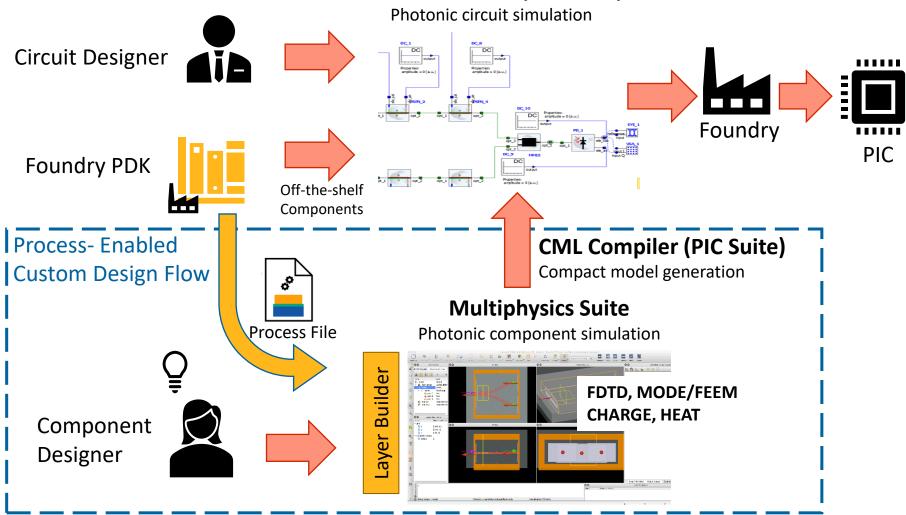

#### Process-enabled Custom Component Design

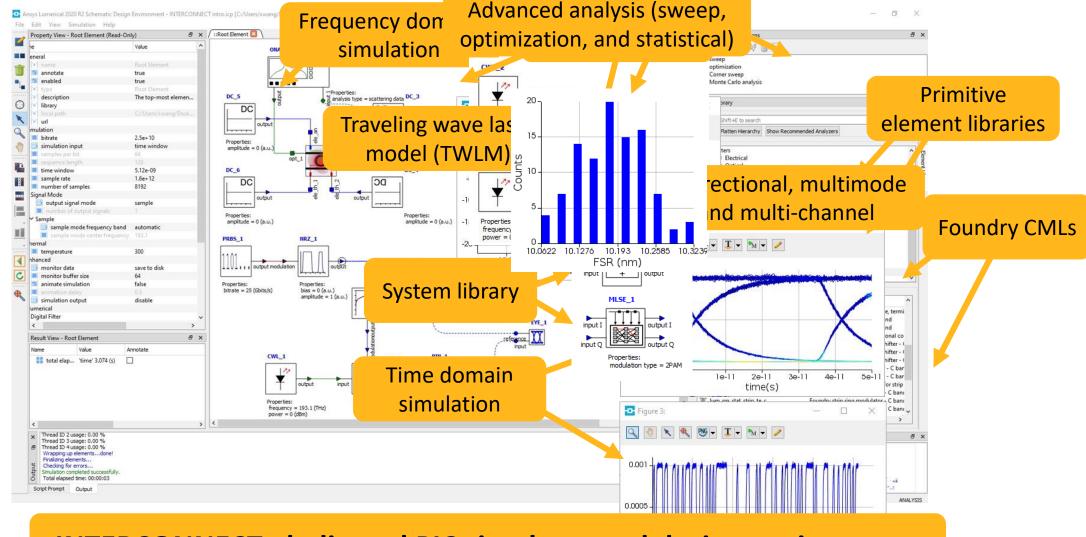

#### **INTERCONNECT (PIC Suite)**

https://www.ansys.com/blog/design-foundry-compatible-photonic-components

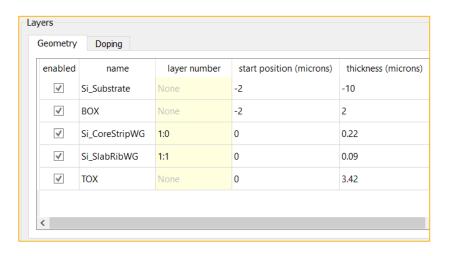

## Foundry Process File Enables Active & Passive Component Design

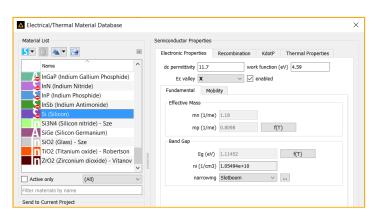

#### **Process Information**

- Layer names and numbers

- Layer thicknesses

- Layer positions

- Material compositions

#### **Material models**

- Electrical material properties

- Thermal material properties

- Optical index perturbation models

- Electrical + thermal stimulus

#### **Doping profile**

- Vertical 1D doping profile for each doping process

- Defined using normal or skewed normal distribution functions

### Design, Simulate, and Extract Component Model

10

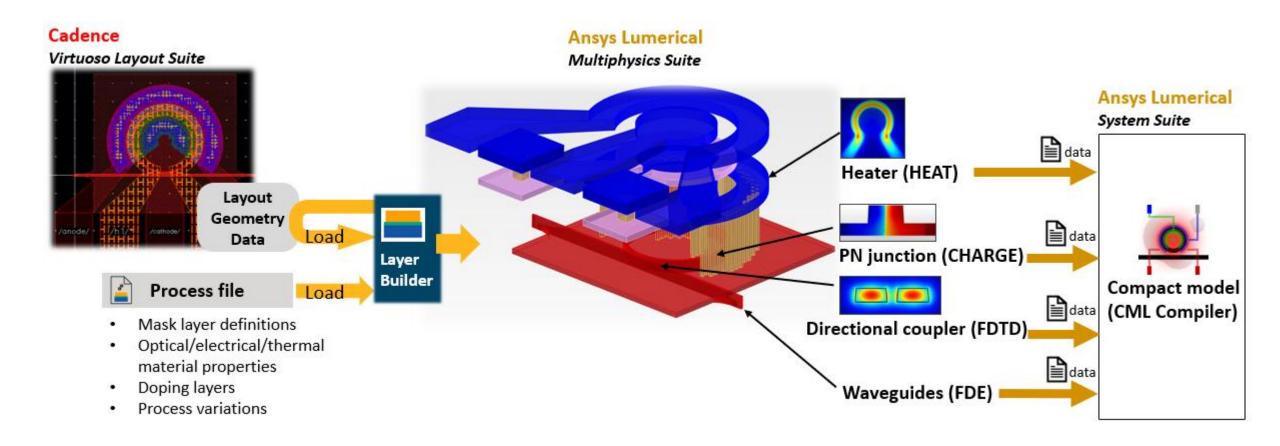

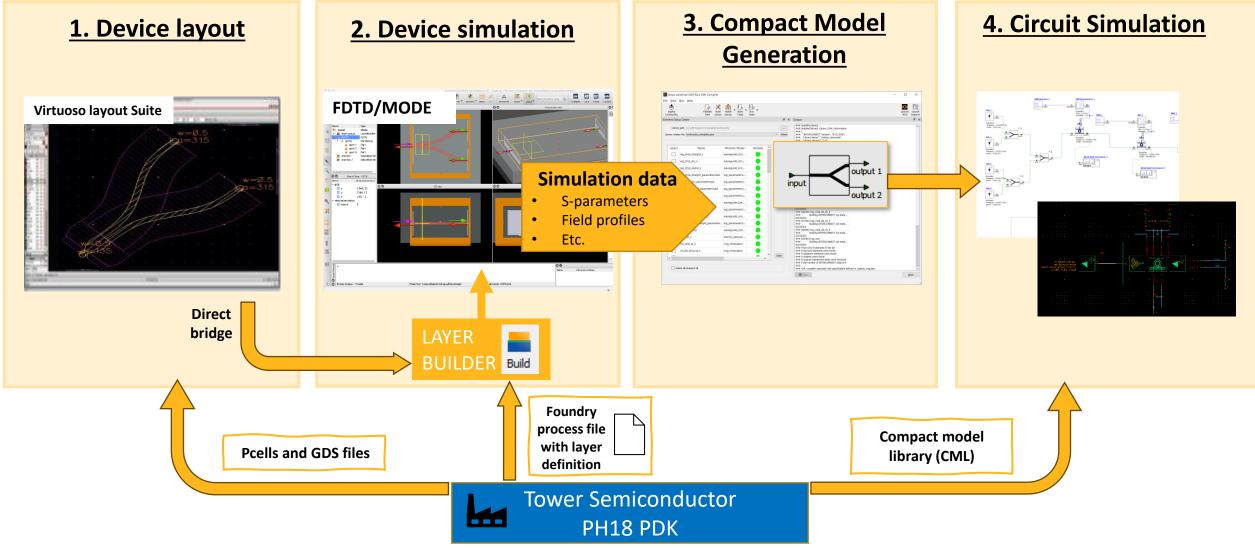

## Tower Semiconductor- Ansys Foundry Compatible Design Flow

©2025 ANSYS, Inc.

# Design of Ring Modulator and DWDM Circuit

Case Study

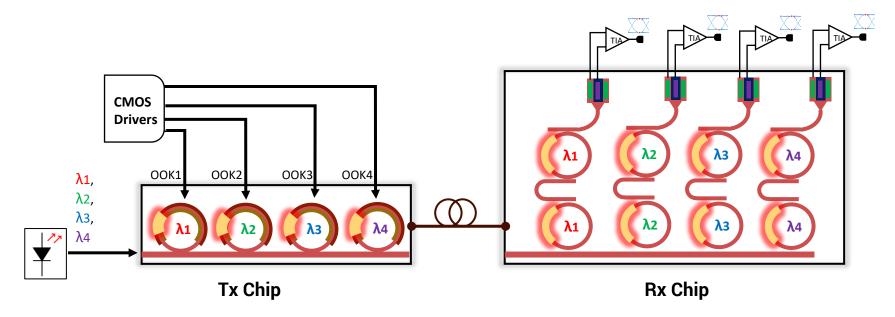

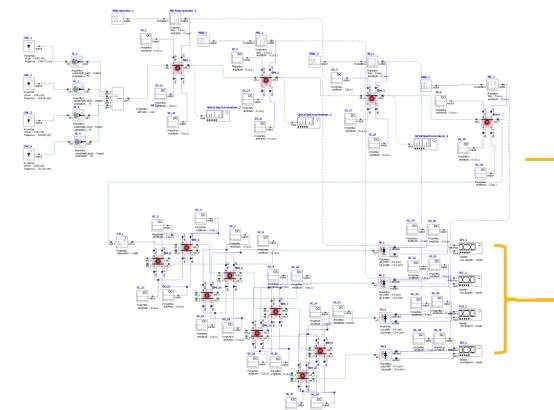

#### DWDM Circuit Simulation with Custom Ring Modulator

- DWDM (dense wavelength division multiplexing) is a popular method for designing photonic transceivers.

- 4-channel DWDM transceiver with CW lasers, transmitter circuit and receiver circuit.

- The key component is the ring modulator that encodes the RF signal onto the photonic carrier signal.

- We will use our custom ring modulator along with other photonic components directly available in the Tower PDK to design and simulate the DWDM circuit.

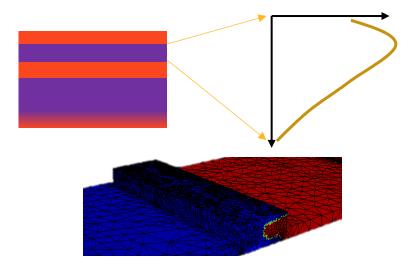

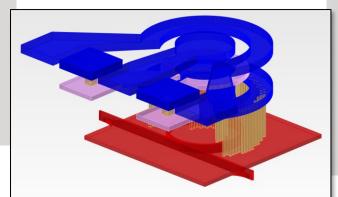

### Ring Modulator Design Enabled by Foundry Process File

#### **Process file**

- Mask layer definitions

- Optical/electrical/thermal material properties

- Doping layers

- **Process variations**

#### **\nsys** Multiphysics Suite

#### FDTD: Directional Coupler

Coupling coefficient

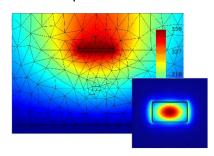

#### **HEAT:** Thermal tuner

- Temperature map

- Thermal Bandwidth

- Heater IV

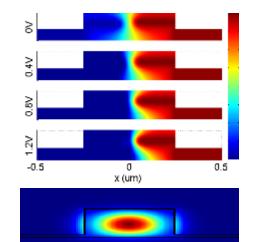

#### **MODE/FEEM:** Waveguides

- **Effective** index

- Group index

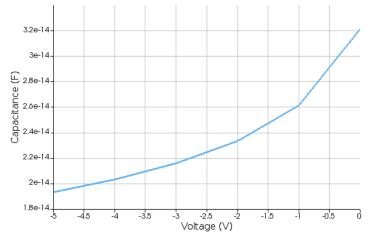

#### **CHARGE:** PN junction

- Charge distribution

- Slab Resistance

- **Junction Capacitance**

**Ansys** CML Compiler: Model data  $\Longrightarrow$  Compact model  $\checkmark$

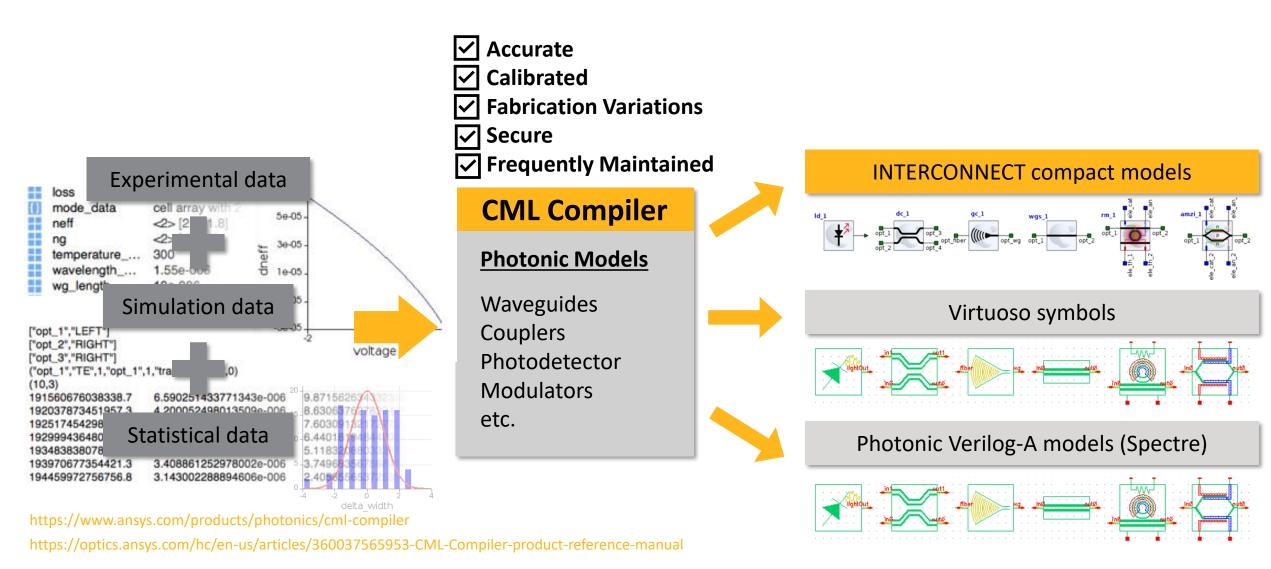

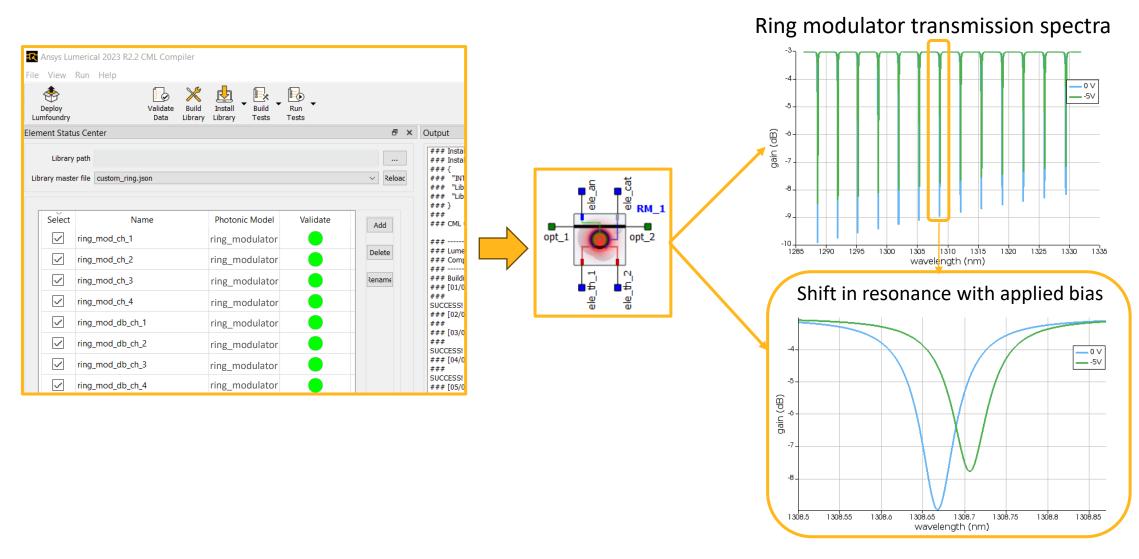

## Compact Model Generation with CML Compiler

#### DWDM Simulation with Lumerical INTERCONNECT

**INTERCONNECT:** dedicated PIC simulator and design environment

# Walkthrough / Demo

#### Overview of the demo

- This workflow has been tested with Tower Semiconductor PH18M process file; however, the files here use a general process file.

- 6 steps demo to the design case mentioned earlier:

- Step 1 Becoming more familiar with Lumerical component level UI

- Step 2 Directional coupler simulation with FDTD

- Step 3 Modulator simulation with CHARGE

- Step 4 Thermal modulation with HEAT

- Step 5 Waveguide simulation with MODE

- Step 6 Creating the compact model with CML Compiler

- Quick mention Circuit simulation with INTC

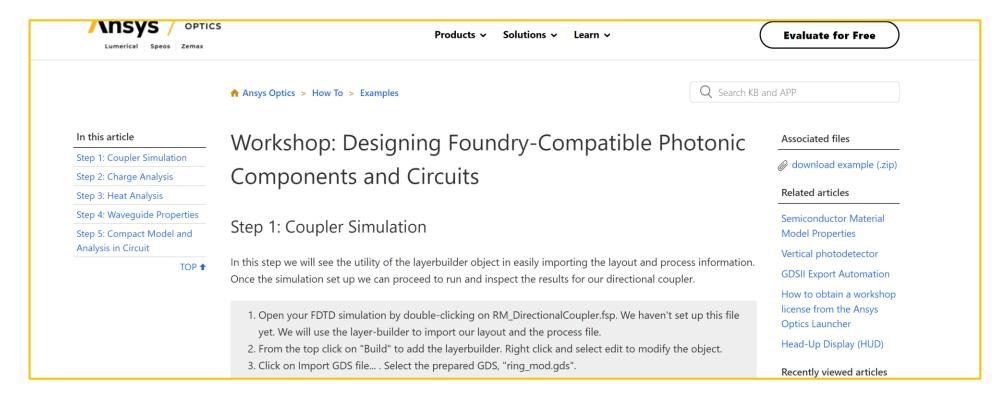

### Testing this demo on your own

- The Workshop licenses, files, and steps to run will remain available until July 18th:

- https://optics.ansys.com/hc/en-us/articles/31257798958611-Workshop-Designing-Foundry-Compatible-Photonic-Components-and-Circuits

# Lumerical UI

Step 1

# Coupler Simulation in FDTD

Step 2

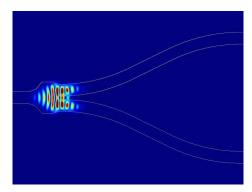

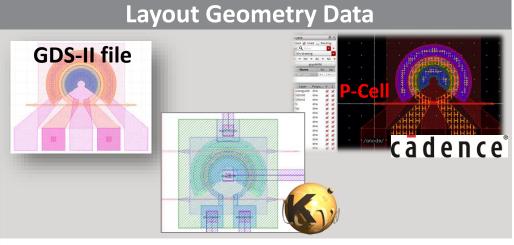

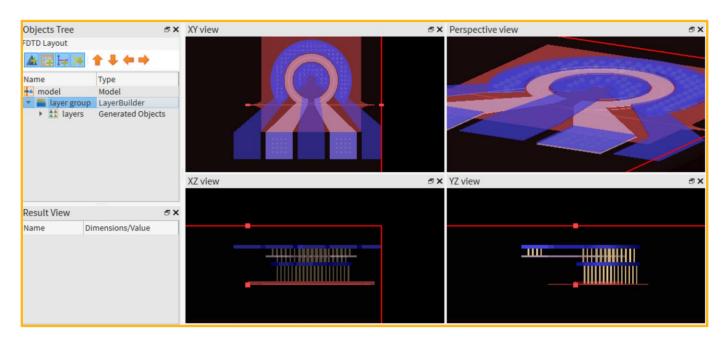

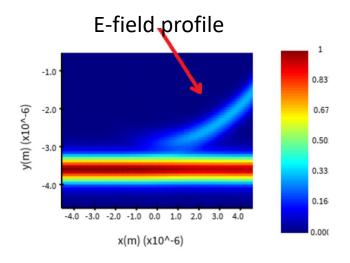

### Step 2: Directional Coupler Simulation with FDTD

- 3D FDTD simulation using layer builder

- Process file

- GDS file for ring modulator design

- S-parameter sweep to extract coupling efficiency

#### Through transmission

# Modulator Simulation in CHARGE

Step 3

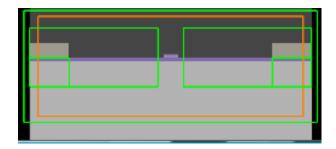

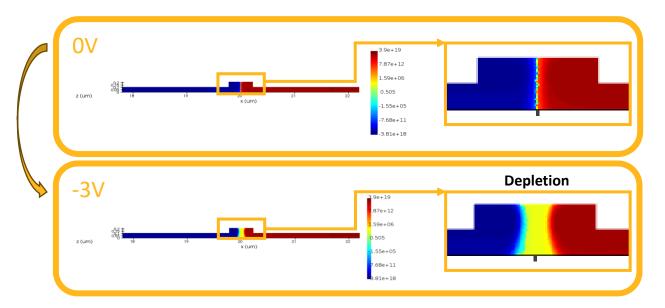

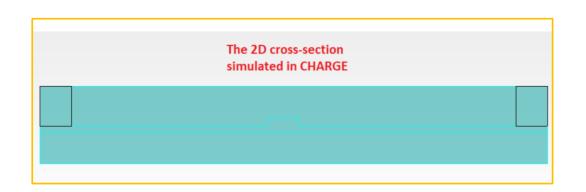

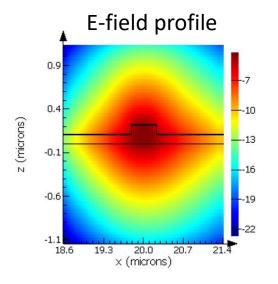

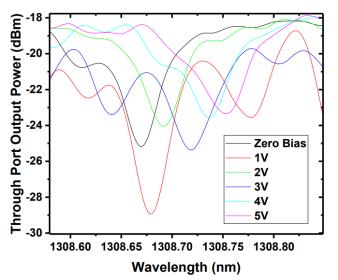

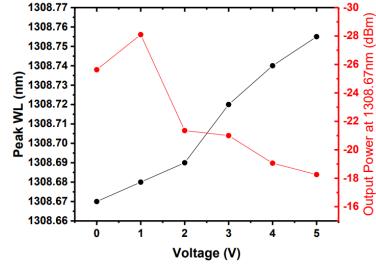

### Step 3: PN Junction Simulation with CHARGE

- 2D CHARGE simulation using layer builder

- Process file

- GDS file for ring modulator design

- Bias voltage swept from 0 V to -3 V to extract charge density profile and electrical characteristic parameters

# Thermal Simulation in HEAT

Step 4

# Waveguide Simulation in MODE

Step 5

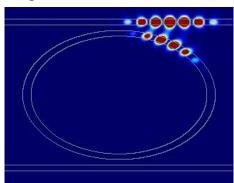

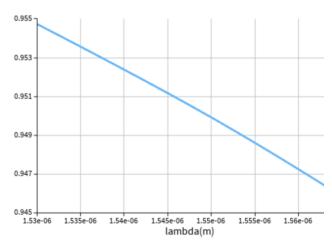

## Step 5: Optical Waveguide Simulation with MODE

- Process file

- GDS file for ring modulator design

- Charge density profile imported from electrical simulation

- Bent waveguide analysis enabled for accurate mode profile calculation

# Creating the Compact Model of your Device

Step 6

## Step 5: Ring Compact Model (CML Compiler → INTERCONNECT)

## Step 5: Calibrated Ring Modulator Compact Model

- CML Compiler enables fine tuning of models based on measurement data.

- The ring\_modulator model supports tuning for resonant wavelength, Q factor, FSR, IL,

ER, thermal and electrical modulation efficiency.

```

"max" : 40000,

"min" : 20000,

"tuning" : 0,

"value" : 29885,

"visible to user" : 0

'mod eff" :

"max" : 1.7e-11,

"min" : 1.7e-11,

"ref1" : 0,

"ref2" : -5.

"tuning" : 1,

'value" : 1.7e-11,

"visible to user" : 0

```

Enable 'tuning' to calibrate model with measurement data for various FOMs

## Circuit Simulation with INTERCONNECT

Quick Mention (Step 7)

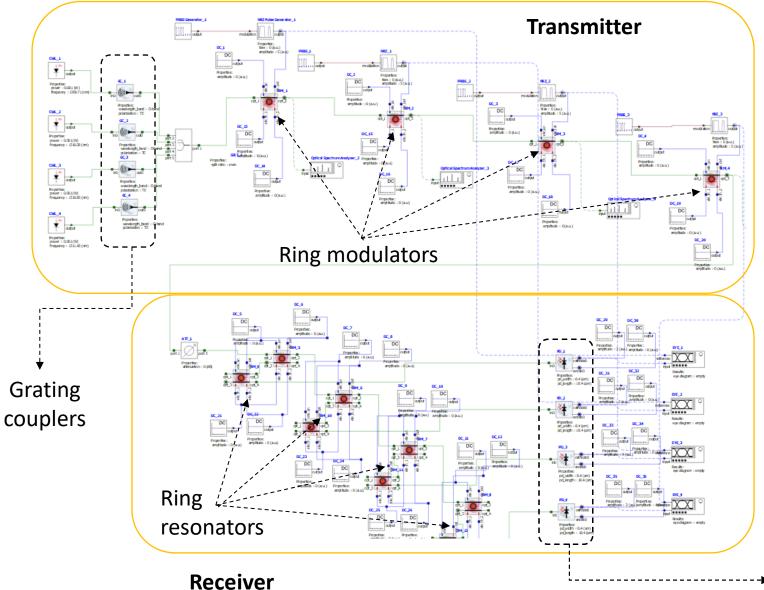

#### **DWDM Circuit Simulation in INTERCONNECT**

- 4-channel DWDM circuit with 100 GHz channel spacing.

- Grating coupler from the PH18 library to couple light from laser sources into the transmitting circuit.

- Custom ring modulator model from CML Compiler for the transmitter.

- Similar custom 4-port ring modulator/resonator for the receiver.

- Photodetector from the PH18 library to convert optical signal into electrical at the receiver end.

**Photodetectors**

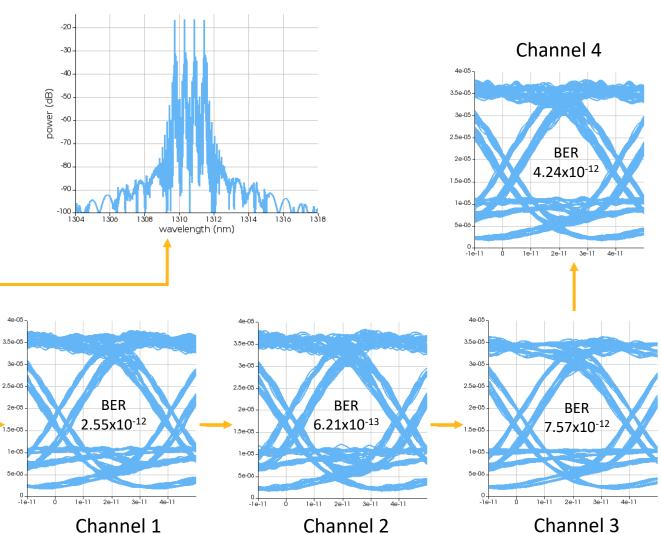

#### **Circuit Simulation Results**

• Bitrate = 25 Gbps

• BER  $\cong 10^{-12}$

#### Transmitting spectrum

# Summary

### Summary

- Ansys and Tower Semiconductor have partnered to enable a complete electro-optic design flow for photonic designers.

- Ansys's layer builder and Tower Semiconductor's process file ensures accurate, foundry compatible design for both passive and active components.

Q & A

# **Ansys**